原理

3位并行比较型A/D转换器的原理电路如图1所示。

它由电阻分压器、电压比较器、寄存器及编码器组成。图中的8个电阻将参考电压REF分成8个等级,其中7个等级的电压分别作为7个比较器C1~C7的参考电压,其数值分别为REF/15、3REF/15…、13REF/15。输入电压为1,它的大小决定各比较器的输出状态,如当0≤1<REF/15时,C7~C1的输出状态都为0;当3REF/15≤1<5REF/15时,比较器C6和C7的输出O6=O7=1,余各比较器的状态均为0。根据各比较器的参考电压值,可以确定输入模拟电压值与各比较器输出状态的关系。

工作原理

比较器的输出状态由D触发器存储,经优先编码器编码,得到数字量输出。优先编码器优先级别最高是7,最低的是1。设1变化范围是0~VREF,输出3位数字量为210,3位并行比较型A/D转换器的输入、输出关系如表1所示。

| 模拟输入 | 比较器输出状态 | 数字输出 |

|---|---|---|

| 0≤1<REF/15 | ||

| REF/15≤1<3REF/15 | ||

| 3REF/15≤1<5REF/15 | ||

| 5REF/15≤1<7REF/15 | ||

| 7REF/15≤1<9REF/15 | ||

| 9REF/15≤1<11REF/15 | ||

| 11REF/15≤1<13REF/15 | ||

| 13REF/15≤1<REF |

特点

改进方法

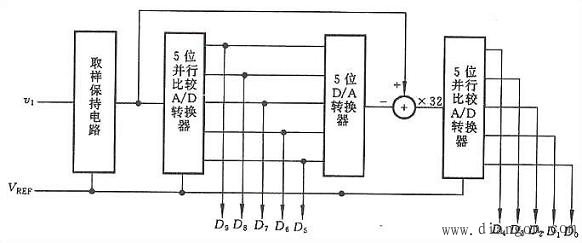

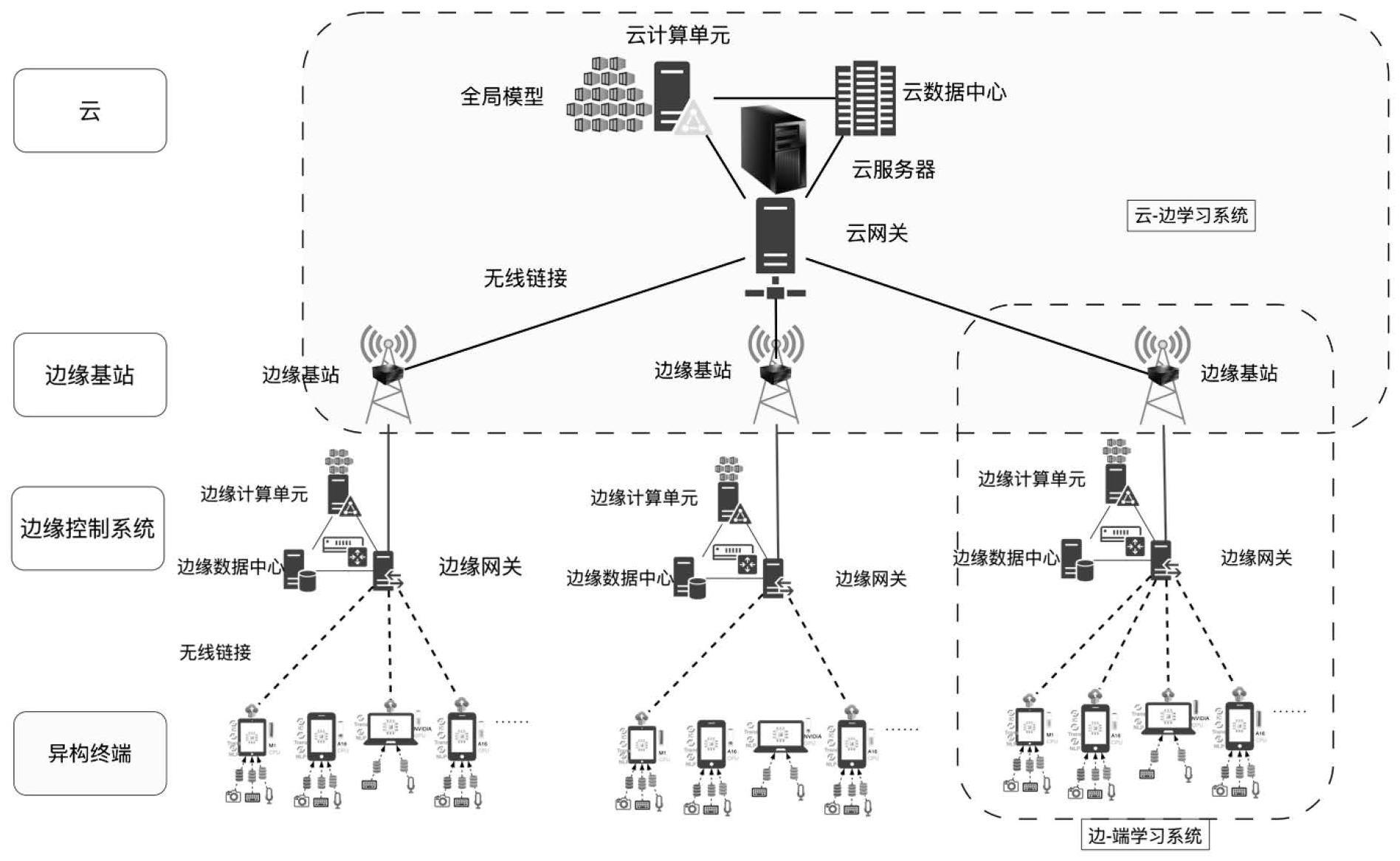

为了解决提高分辨率和增加元件数的矛盾,可以采取分级并行转换的方法。10位分级并行A/D转换原理如图2所示。

图中输入模拟信号v1,经取样-保持电路后分两路,一路先经第一级5位并行A/D转换进行粗转换得到输出数字量的高5位,另一路送至减法器,与高5位D/A转换得到的模拟电压相减。由于相减所得到的差值电压小于1LSB,为保证第二级A/D转换器的转换精度,将差值放大25=32倍,送第二级5位并行比较A/D转换器,得到低5位输出。这种方法虽然在速度上作了牺牲,却使元件数大为减少,在需要兼顾分辨率和速度的情况下常被采用。

一、积分型 积分型AD的工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。二、逐次比较型逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。其电路规模属于中等。其优点是速度较高、功耗低,在低分辨率(<12位)时价格便宜,但高精度(>12位)时价格很高。三、并行比较型/串并行比较型 并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称Flash(快速)型。由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。还有分成三步或多步实现AD转换的称为分级型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。这类AD速度比逐次比较型高,电路规模比并行型小。四、Σ-Δ调制型 Σ-Δ调制型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。原理上近似于积分型,将输入电压转换成时间(脉冲宽度)信号,用数字滤波器处理后得到数字值。电路的数字部分基本上容易单片化,因此容易做到高分辨率。主要用于音频和测量。五、电容阵列逐次比较型 电容阵列逐次比较型AD在内置DA转换器中采用电容矩阵方式,也可称为电荷再分配型。一般的电阻阵列DA转换器中多数电阻的值必须一致,在单芯片上生成高精度的电阻并不容易。如果用电容阵列取代电阻阵列,可以用低廉成本制成高精度单片AD转换器。最近的逐次比较型AD转换器大多为电容阵列式的。六、压频变换型 压频变换型是通过间接转换方式实现模数转换的。其原理是首先将输入的模拟信号转换成频率,然后用计数器将频率转换成数字量。从理论上讲这种AD的分辨率几乎可以无限增加,只要采样的时间能够满足输出频率分辨率要求的累积脉冲个数的宽度。其优点是分辨率高、功耗低、价格低,但是需要外部计数电路共同完成AD转换。

本文原创来源:电气TV网,欢迎收藏本网址,收藏不迷路哦!

添加新评论