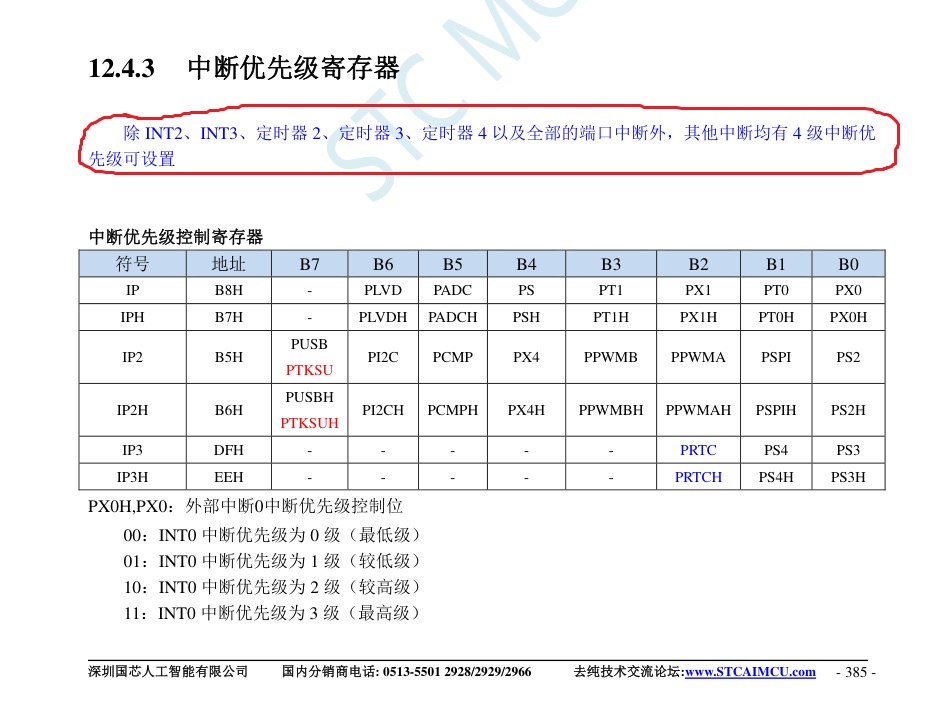

中断优先级设置是一种技术,它为中断分配优先级,以确保根据其严重性及时处理它们。当多个中断同时发生时,优先级较高的中断会优先处理。

中断优先级的类型

有多种中断优先级类型,包括:

- 固定优先级:每个中断都分配了一个固定的优先级,该优先级永远不会改变。

- 动态优先级:中断的优先级可以根据系统状态动态改变。

- 可抢占式优先级:具有较高优先级的中断可以抢先具有较低优先级的中断。

- 非抢占式优先级:具有较低优先级的中断无法抢先具有较高优先级的中断。

中断优先级设置的好处

中断优先级设置提供了许多好处,包括:- 确保及时处理关键中断:通过为关键中断分配更高的优先级,可以确保即使在系统繁忙时也能及时处理。

- 减少中断延迟:通过优先处理高优先级中断,可以减少中断延迟,从而提高系统响应能力。

- 防止系统崩溃:通过优先处理关键中断,可以防止系统崩溃,因为这些中断对于系统正常运行至关重要。

中断优先级设置的缺点

中断优先级设置也有一些缺点,包括:- 可能导致优先级反转:优先级反转会发生在低优先级中断阻止高优先级中断时,这可能会导致系统性能下降。

- 可能增加系统复杂性:中断优先级设置可能增加系统复杂性,因为需要考虑多个中断的优先级。

- 可能产生死锁:如果两个或更多中断互相阻止,则可能导致死锁,使系统无法正常运行。

中断优先级设置的应用

中断优先级设置在各种应用中都很重要,包括:- 实时系统:在实时系统中,及时处理中断至关重要,因此中断优先级设置对于确保满足时序要求至关重要。

- 嵌入式系统:嵌入式系统通常具有有限的资源,因此中断优先级设置对于优化系统性能至关重要。

- 多处理器系统:在多处理器系统中,中断优先级设置对于协调处理器之间的中断处理至关重要。

结论

中断优先级设置是一种重要的技术,它可以确保及时处理中断并提高系统性能。虽然中断优先级设置有一些缺点,但其好处通常大于缺点。通过考虑中断的严重性并仔细配置中断优先级,可以优化系统响应能力和可靠性。设置中断优先级的函数,CMISIS已经写好,并嵌入到了编译器中,例如,我们用KEIL开发的话,设置中断优先级的函数位于core_cm0.h文件当中,函数如下所示:/** \brief Set Interrupt PriorityThe function sets the priority of an interrupt.\note The priority cannot be set for every core interrupt.\param [in] IRQn Interrupt number.\param [in] priority Priority to set.*/__STATIC_INLINE void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority){if(IRQn < 0) {SCB->SHP[_SHP_IDX(IRQn)] = (SCB->SHP[_SHP_IDX(IRQn)] & ~(0xFF << _BIT_SHIFT(IRQn))) |(((priority << (8 - __NVIC_PRIO_BITS)) & 0xFF) << _BIT_SHIFT(IRQn)); }else {NVIC->IP[_IP_IDX(IRQn)] = (NVIC->IP[_IP_IDX(IRQn)] & ~(0xFF << _BIT_SHIFT(IRQn))) |(((priority << (8 - __NVIC_PRIO_BITS)) & 0xFF) << _BIT_SHIFT(IRQn)); }}从上面函数可以看出,该函数有两个参数,IRQn是指要设置的中断向量,priority是中断优先级,优先级可以是0 1 2 3四个数,0的优先级最大,3的优先级最小。 假设你要设置GPIO1中断的优先级最高,那么就是:NVIC_SetPriority(EINT1_IRQn, 0);这时,有人会问,”EINT1_IRQn”答:这个可以在LPC11xx.h文件当中找到,如下所示:/** ==========================================================================* ---------- Interrupt Number Definition -----------------------------------* ==========================================================================*/typedef enum IRQn{/****** Cortex-M0 Processor Exceptions Numbers ***************************************************/Reset_IRQn = -15, /*!< 1 Reset Vector, invoked on Power up and warm reset */NonMaskableInt_IRQn = -14, /*!< 2 Non maskable Interrupt, cannot be stopped or preempted */HardFault_IRQn = -13, /*!< 3 Hard Fault, all classes of Fault */SVCall_IRQn = -5, /*!< 11 System Service Call via SVC instruction */PendSV_IRQn = -2, /*!< 14 Pendable request for system service */SysTick_IRQn = -1, /*!< 15 System Tick Timer *//****** LPC11Cxx or LPC11xx Specific Interrupt Numbers *******************************************************/WAKEUP0_IRQn = 0, /*!< All I/O pins can be used as wakeup source. */WAKEUP1_IRQn = 1, /*!< There are 13 pins in total for LPC11xx */WAKEUP2_IRQn = 2,WAKEUP3_IRQn = 3,WAKEUP4_IRQn = 4,WAKEUP5_IRQn = 5,WAKEUP6_IRQn = 6,WAKEUP7_IRQn = 7,WAKEUP8_IRQn = 8,WAKEUP9_IRQn = 9,WAKEUP10_IRQn = 10,WAKEUP11_IRQn = 11,WAKEUP12_IRQn = 12,CAN_IRQn = 13, /*!< CAN Interrupt */SSP1_IRQn = 14, /*!< SSP1 Interrupt */I2C_IRQn = 15, /*!< I2C Interrupt */TIMER_16_0_IRQn = 16, /*!< 16-bit Timer0 Interrupt */TIMER_16_1_IRQn = 17, /*!< 16-bit Timer1 Interrupt */TIMER_32_0_IRQn = 18, /*!< 32-bit Timer0 Interrupt */TIMER_32_1_IRQn = 19, /*!< 32-bit Timer1 Interrupt */SSP0_IRQn = 20, /*!< SSP0 Interrupt */UART_IRQn = 21, /*!< UART Interrupt */Reserved0_IRQn = 22, /*!< Reserved Interrupt */Reserved1_IRQn = 23,ADC_IRQn = 24, /*!< A/D Converter Interrupt */WDT_IRQn = 25, /*!< Watchdog timer Interrupt */BOD_IRQn = 26, /*!< Brown Out Detect(BOD) Interrupt */FMC_IRQn = 27, /*!< Flash Memory Controller Interrupt */EINT3_IRQn = 28, /*!< External Interrupt 3 Interrupt */EINT2_IRQn = 29, /*!< External Interrupt 2 Interrupt */EINT1_IRQn = 30, /*!< External Interrupt 1 Interrupt */EINT0_IRQn = 31, /*!< External Interrupt 0 Interrupt */} IRQn_Type;

本文原创来源:电气TV网,欢迎收藏本网址,收藏不迷路哦!

添加新评论